## Parallel pointer analysis for large-scale software

## Author:

Su, Yu

**Publication Date:** 2015

DOI: https://doi.org/10.26190/unsworks/18164

## License:

https://creativecommons.org/licenses/by-nc-nd/3.0/au/ Link to license to see what you are allowed to do with this resource.

Downloaded from http://hdl.handle.net/1959.4/54374 in https:// unsworks.unsw.edu.au on 2024-05-03

# Parallel Pointer Analysis for Large-Scale

## Software

by

## Yu Su

## A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

IN THE SCHOOL

OF

Computer Science and Engineering

THE UNIVERSITY OF NEW SOUTH WALES

SYDNEY · AUSTRALIA

April 29, 2015

All rights reserved. This work may not be

reproduced in whole or in part, by photocopy

or other means, without the permission of the author.

$\bigodot$ Yu Su 2015

|                                                                         | SITY OF NEW SOUTH WALES<br>is/Dissertation Sheet |

|-------------------------------------------------------------------------|--------------------------------------------------|

| Surname or Family name: Su                                              |                                                  |

| First name: Yu                                                          | Other name/s:                                    |

| Abbreviation for degree as given in the University calendar: <b>PhD</b> |                                                  |

| School: School of Computer Science and<br>Engineering                   | Faculty: Faculty of Engineering                  |

| Title: Parallel Pointer Analysis for Large-Scale<br>Software            |                                                  |

#### Abstract 350 words maximum: (PLEASE TYPE)

Pointer analysis, a process that statically computes the possible runtime values of a pointer in a program, enables the understanding of program behaviours. It lies in the heart of software engineering and has laid foundations for extensive applications, such as compiler optimisation, software bug detection and program verification. The long existing challenge of the analysis, however, is to improve its efficiency while maintaining high precision, especially when applied to large programs.

Parallel platforms, which are prevalent nowadays, provide a great opportunity to enhance the efficiency of pointer analysis. Yet, it is challenging to parallelise this analysis, which is essentially an irregular graph algorithm. In general, pointer analysis comes in two styles: whole-program and demand-driven. Whole-program analysis, which computes the points-to information of all variables in a program, is often formulated as a graph-rewriting problem that makes extensive modifications to data structures representing the graph. Demand-driven analysis, which only targets the variables requested by queries, is solved in terms of a graph traversal problem.

This thesis presents the design and implementation of a parallel pointer analysis framework that enables efficient pointer analysis for large-scale software. This framework consists of three parts, each targeting one of today's most popular parallel platforms, and is implemented with a combination of Java, C++ and CUDA. The first part is a parallel solution to pointer analysis driven by queries, on multicore CPUs. It has achieved significant speedups over the sequential solution, since a large amount of unnecessary graph traversals have been eliminated by information sharing and query scheduling. The second part is an efficient GPU solution to whole-program pointer analysis. With effective load balancing and reduced redundant computation, it demonstrates considerable speedups over the state-of-the-art GPU implementation. The third part is a heterogeneous CPU-GPU solution to whole-program pointer analysis. It prioritises the distribution of different workloads to CPU/GPU according to the processing unit's ability for processing them, and therefore has achieved speedups over the corresponding CPU-only and GPU-only solutions. The effectiveness of each part of the framework is demonstrated via an evaluation with a set of open-source Java/C programs.

#### Declaration relating to disposition of project thesis/dissertation

I hereby grant to the University of New South Wales or its agents the right to archive and to make available my thesis or dissertation in whole or in part in the University libraries in all forms of media, now or here after known, subject to the provisions of the Copyright Act 1968. I retain all property rights, such as patent rights. I also retain the right to use in future works (such as articles or books) all or part of this thesis or dissertation.

I also authorise University Microfilms to use the 350 word abstract of my thesis in Dissertation Abstracts International (this is applicable to doctoral theses only).

|            |                | • •      |         |

|------------|----------------|----------|---------|

| M          | 1              |          |         |

| - 1        | M              | l l      |         |

| <i>6</i> N | $/\mathcal{N}$ | <b>\</b> | • • • • |

Signature

Witness

29/04/2015 ..... Date

The University recognises that there may be exceptional circumstances requiring restrictions on copying or conditions on use. Requests for restriction for a period of up to 2 years must be made in writing. Requests for a longer period of restriction may be considered in exceptional circumstances and require the approval of the Dean of Graduate Research.

FOR OFFICE USE ONLY

Date of completion of requirements for Award:

#### **ORIGINALITY STATEMENT**

'I hereby declare that this submission is my own work and to the best of my knowledge it contains no materials previously published or written by another person, or substantial proportions of material which have been accepted for the award of any other degree or diploma at UNSW or any other educational institution, except where due acknowledgement is made in the thesis. Any contribution made to the research by others, with whom I have worked at UNSW or elsewhere, is explicitly acknowledged in the thesis. I also declare that the intellectual content of this thesis is the product of my own work, except to the extent that assistance from others in the project's design and conception or in style, presentation and linguistic expression is acknowledged.'

Signed

Ju/m

29/04/2015

Date

### **COPYRIGHT STATEMENT**

<sup>1</sup> hereby grant the University of New South Wales or its agents the right to archive and to make available my thesis or dissertation in whole or part in the University libraries in all forms of media, now or here after known, subject to the provisions of the Copyright Act 1968. I retain all proprietary rights, such as patent rights. I also retain the right to use in future works (such as articles or books) all or part of this thesis or dissertation.

I also authorise University Microfilms to use the 350 word abstract of my thesis in Dissertation Abstract International (this is applicable to doctoral theses only).

I have either used no substantial portions of copyright material in my thesis or I have obtained permission to use copyright material; where permission has not been granted I have applied/will apply for a partial restriction of the digital copy of my thesis or dissertation.

Signed

29/04/2015

Date

### AUTHENTICITY STATEMENT

'I certify that the Library deposit digital copy is a direct equivalent of the final officially approved version of my thesis. No emendation of content has occurred and if there are any minor variations in formatting, they are the result of the conversion to digital format.'

Signed

29/04/2015

Date

## Abstract

Pointer analysis, a process that statically computes the possible runtime values of a pointer in a program, enables the understanding of program behaviours. It lies in the heart of software engineering and has laid foundations for extensive applications, such as compiler optimisation, software bug detection and program verification. The long existing challenge of the analysis, however, is to improve its efficiency while maintaining high precision, especially when applied to large programs.

Parallel platforms, which are prevalent nowadays, provide a great opportunity to enhance the efficiency of pointer analysis. Yet, it is challenging to parallelise this analysis, which is essentially an irregular graph algorithm. In general, pointer analysis comes in two styles: whole-program and demand-driven. Whole-program analysis, which computes the points-to information of all variables in a program, is often formulated as a graph-rewriting problem that makes extensive modifications to data structures representing the graph. Demand-driven analysis, which only targets the variables requested by queries, is solved in terms of a graph traversal problem.

This thesis presents the design and implementation of a parallel pointer analysis framework that enables efficient pointer analysis for large-scale software. This framework consists of three parts, each targeting one of today's most popular parallel platforms, and is implemented with a combination of Java, C++ and CUDA. The first part is a parallel solution to pointer analysis driven by queries, on multicore CPUs. It has achieved significant speedups over the sequential solution, since a large amount of unnecessary graph traversals have been eliminated by information sharing and query scheduling. The second part is an efficient GPU solution to whole-program pointer analysis. With effective load balancing and reduced redundant computation, it demonstrates considerable speedups over the state-of-the-art GPU implementation. The third part is a heterogeneous CPU-GPU solution to whole-program pointer analysis. It prioritises the distribution of different workloads to CPU/GPU according to the processing unit's ability for processing them, and therefore has achieved speedups over the corresponding CPU-only and GPUonly solutions. The effectiveness of each part of the framework is demonstrated via an evaluation with a set of open-source Java/C programs.

## **Publications**

- Yu Su, Ding Ye, Jingling Xue and Xiangke Liao. An Efficient GPU Implementation of Inclusion-based Pointer Analysis. *IEEE Transactions on Parallel and Distributed Systems (TPDS '15). To Appear.*

- Ding Ye, Yu Su, Yulei Sui and Jingling Xue. WPBound: Enforcing Spatial Memory Safety Efficiently at Runtime with Weakest Preconditions. *IEEE International Symposium on Software Reliability Engineering (ISSRE '14).*

- Yu Su, Ding Ye and Jingling Xue. Parallel Pointer Analysis with CFL-Reachability. *IEEE International Conference on Parallel Processing (ICPP* '14).

- Yu Su, Ding Ye and Jingling Xue. Accelerating Inclusion-based Pointer Analysis on Heterogeneous CPU-GPU Systems. *IEEE International Confer*ence on High Performance Computing (HiPC '13).

- Peng Di, Ding Ye, Yu Su, Yulei Sui and Jingling Xue. Automatic Parallelization of Tiled Loop Nests with Enhanced Fine-Grained Parallelism on GPUs. *IEEE International Conference on Parallel Processing (ICPP '12)*.

## Acknowledgements

First and foremost, I would like to express my deepest gratefulness to my supervisor, Prof. Jingling Xue. He is always there, ready to help me in all aspects, from the very beginning when I applied for a PhD. Through all stages of my doctoral study, his broad knowledge and sharp insight have kept me on track of an interesting and challenging research path. He spares no effort in teaching me how to think and write. Looking back at the three and half years at the CORG group, I feel amazed how much time and energy he has spent in inspiring and guiding me. My sincere gratitude also goes to the funding I received towards PhD: the UNSW Tuition Fee Scholarship, and a research stipend from my supervisor.

I am very much thankful to Ding Ye, my husband and colleague, for his unconditional love and support through my entire doctoral study. Without his great patience and effort, my path towards PhD would not have been so smooth and delightful. Without his continuous encouragement, I would not have had such advances in my personal and career development.

I would like to thank Dr. Peng Di for his dedicated collaboration on my work. He surprises me by how good he is at coming up with new ideas. Thank Dr. Yulei Sui for his willingness to share and help. His strength in programming and thirst for communication have inspired me a lot. I also give my sincere thanks to other colleagues from the CORG group, Xinwei Xie, Lei Shang, Sen Ye, Yue Li, Hao Zhou, Xiaokang Fan, Tian Tan, Hua Yan, and Feng Zhang. It was a pleasant experience to work with them all during these unforgettable days.

Thank Yu Chen, my best friend, for accompanying me through my PhD study. She encourages and supports me whenever I am down and shows me the positive side. She is always ready to share her great experience to me, from which I benefit greatly.

Lastly, I would like to give my gratefulness and love to my mom and dad for their unconditional love that gives me everything I need.

# Contents

| A                | bstra  | nct                                               | i   |

|------------------|--------|---------------------------------------------------|-----|

| $\mathbf{P}_{1}$ | ublic  | ations                                            | iii |

| A                | cknov  | wledgements                                       | iv  |

| Li               | ist of | Figures                                           | xi  |

| $\mathbf{Li}$    | ist of | Tables 2                                          | xii |

| $\mathbf{Li}$    | ist of | Algorithms x                                      | iii |

| 1                | Intr   | roduction                                         | 1   |

|                  | 1.1    | Challenges                                        | 2   |

|                  | 1.2    | Our Approaches                                    | 4   |

|                  | 1.3    | Contributions                                     | 6   |

|                  | 1.4    | Thesis Organisation                               | 7   |

| <b>2</b>         | Bac    | kground                                           | 9   |

|                  | 2.1    | Whole-Program Pointer Analysis                    | 9   |

|                  |        | 2.1.1 Andersen's Inclusion-based Pointer Analysis | 9   |

|                  |        | 2.1.2 State-of-the-Art                            | 15  |

|   | 2.2 | Dema   | nd-Driven Pointer Analysis              | 18 |

|---|-----|--------|-----------------------------------------|----|

|   |     | 2.2.1  | Program Representation                  | 19 |

|   |     | 2.2.2  | CFL-Reachability-based Pointer Analysis | 20 |

| 3 | Der | nand-l | Driven Analysis on Multi-CPUs           | 26 |

|   | 3.1 | Metho  | odology                                 | 26 |

|   |     | 3.1.1  | A Naive Parallelisation Strategy        | 27 |

|   |     | 3.1.2  | Data Sharing                            | 27 |

|   |     | 3.1.3  | Query Scheduling                        | 32 |

|   | 3.2 | Evalua | ation                                   | 36 |

|   |     | 3.2.1  | Implementations                         | 36 |

|   |     | 3.2.2  | Experimental Settings                   | 37 |

|   |     | 3.2.3  | Methodology                             | 37 |

|   |     | 3.2.4  | Performance Results                     | 39 |

|   | 3.3 | Relate | ed Work                                 | 46 |

|   | 3.4 | Chapt  | ter Summary                             | 46 |

| 4 | Wh  | ole-Pr | ogram Analysis on GPU                   | 48 |

|   | 4.1 | Challe | enges and Motivation                    | 48 |

|   |     | 4.1.1  | Load Imbalance                          | 49 |

|   |     | 4.1.2  | Redundant Traversals                    | 50 |

|   | 4.2 | Metho  | odology                                 | 51 |

|   |     | 4.2.1  | Imbalance-Aware Workload Partitioning   | 51 |

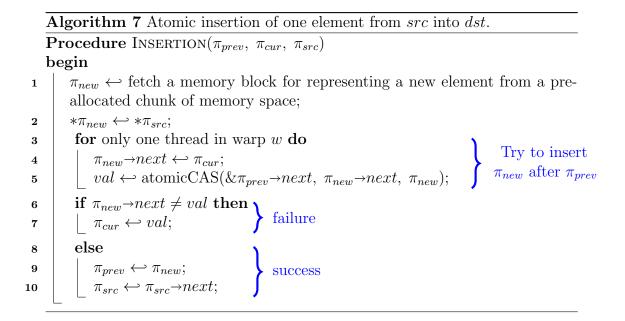

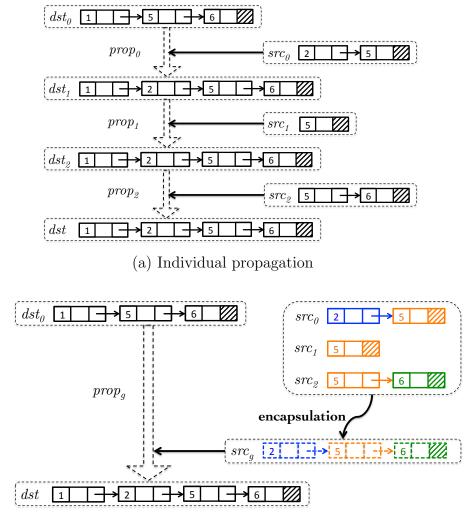

|   |     | 4.2.2  | Adaptive Group Propagation              | 59 |

|   | 4.3 | Evalu  | ation                                   | 65 |

|   |     | 4.3.1  | Methodology and Benchmarks              | 66 |

|   |     | 4.3.2  | Experimental Settings                   | 67 |

|   |     |        |                                         |    |

|          |     | 4.3.3   | Speedups                                                    | 69  |

|----------|-----|---------|-------------------------------------------------------------|-----|

|          |     | 4.3.4   | Effectiveness of Workload Balancing                         | 70  |

|          |     | 4.3.5   | Effectiveness of Adaptive Group Propagation                 | 72  |

|          |     | 4.3.6   | Comparing with a Parallel CPU Implementation                | 74  |

|          | 4.4 | Relate  | d Work                                                      | 75  |

|          |     | 4.4.1   | Sequential Andersen's Analysis                              | 75  |

|          |     | 4.4.2   | Parallel Pointer Analysis                                   | 76  |

|          |     | 4.4.3   | Parallel Graph Algorithms                                   | 77  |

|          | 4.5 | Chapt   | er Summary                                                  | 78  |

| <b>5</b> | Wh  | ole-Pro | ogram Analysis on Heterogeneous CPU-GPU                     | 79  |

|          | 5.1 | Motiva  | ation                                                       | 80  |

|          | 5.2 | Metho   | d                                                           | 81  |

|          |     | 5.2.1   | Graph Data Representation                                   | 82  |

|          |     | 5.2.2   | Managing Communication between CPU and GPU $\ . \ . \ .$    | 82  |

|          |     | 5.2.3   | Partitioning Computation for CPU and GPU                    | 85  |

|          | 5.3 | Optim   | isations                                                    | 91  |

|          |     | 5.3.1   | Optimisation I: On Hiding Communication Overhead            | 91  |

|          |     | 5.3.2   | Optimisation II: On $\Delta P$ -Equivalence and $R_{store}$ | 92  |

|          |     | 5.3.3   | Optimisation III: On Adaptive Heterogeneity                 | 92  |

|          | 5.4 | Evalua  | ation                                                       | 92  |

|          |     | 5.4.1   | Implementations                                             | 93  |

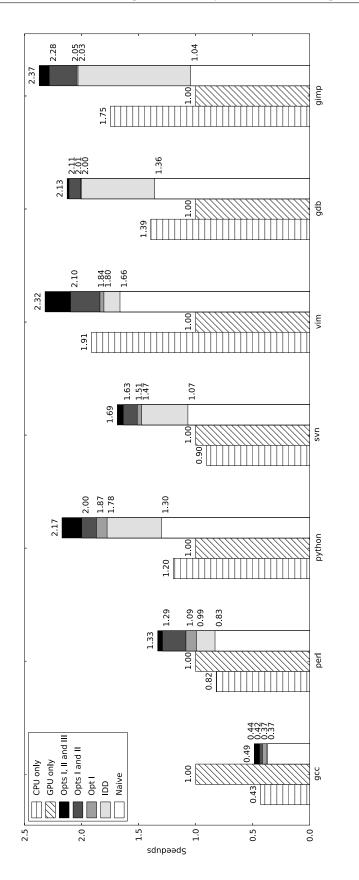

|          |     | 5.4.2   | Speedups                                                    | 95  |

|          |     | 5.4.3   | Dynamic Workload Balancing                                  | 97  |

|          |     | 5.4.4   | Optimisations                                               | 98  |

|          |     | 5.4.5   | Overall Effectiveness                                       | 100 |

|          | 5.5 | Relate  | d Work                                                      | 100 |

|    | 5.6    | Chapter Summary          | 101 |

|----|--------|--------------------------|-----|

| 6  | Con    | clusions and Future Work | 102 |

|    | 6.1    | Conclusions              | 102 |

|    | 6.2    | Future Work              | 106 |

| Bi | ibliog | graphy                   | 108 |

# List of Figures

| 2.1 | An example illustrating Andersen's analysis                                                         | 14 |

|-----|-----------------------------------------------------------------------------------------------------|----|

| 2.2 | Sparse bit vector representing $\{958, 1920\}$                                                      | 17 |

| 2.3 | Syntax of PAG (pointer assignment graph).                                                           | 19 |

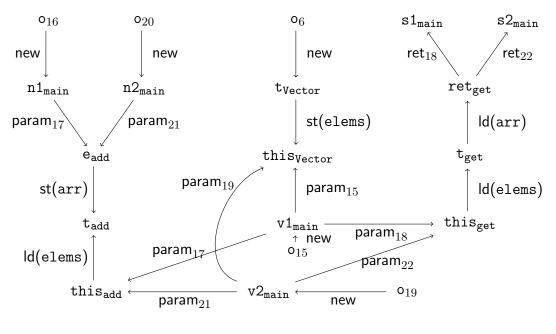

| 2.4 | A Java example and its PAG                                                                          | 21 |

| 3.1 | Adding jmp edges by graph rewriting                                                                 | 29 |

| 3.2 | Syntax of extended PAG                                                                              | 30 |

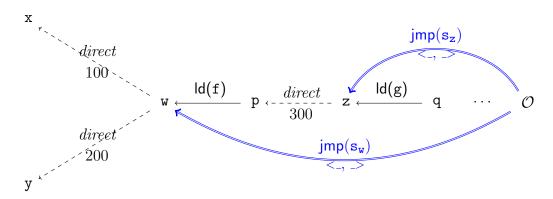

| 3.3 | An example of query scheduling                                                                      | 35 |

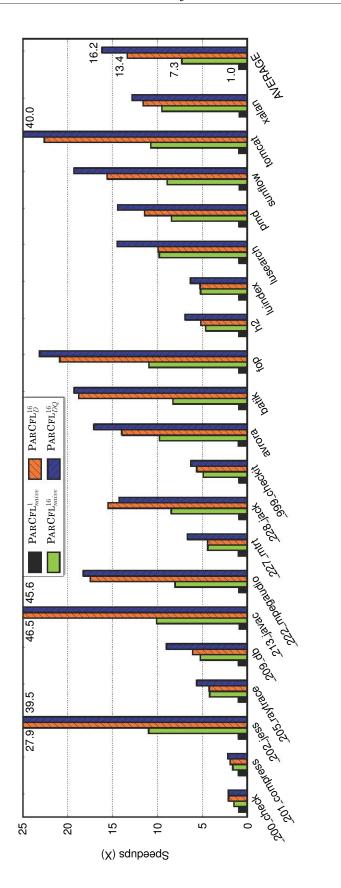

| 3.4 | Speedups of our parallel implementation                                                             | 40 |

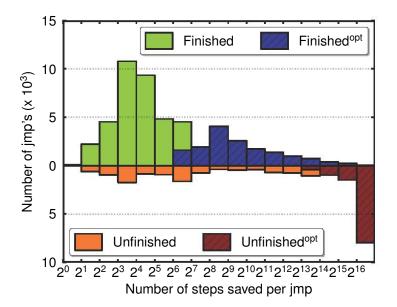

| 3.5 | Histograms of jmp edges                                                                             | 43 |

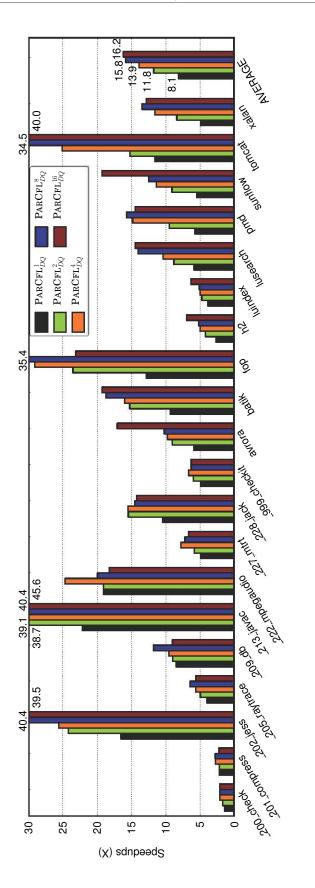

| 3.6 | Speedups of our parallel modes with different numbers of threads                                    | 44 |

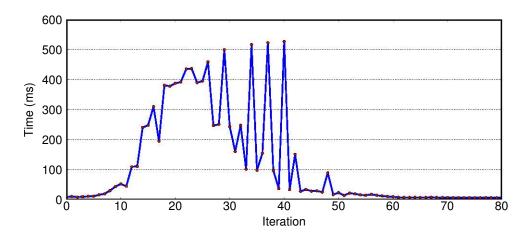

| 4.1 | Execution times of all iterations in vim                                                            | 49 |

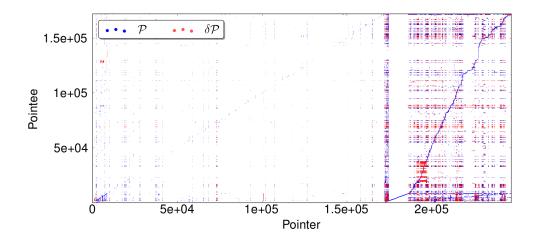

| 4.2 | The points-to edges for vim                                                                         | 50 |

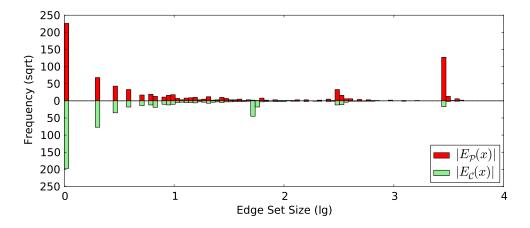

| 4.3 | Distributions of non-zero outgoing degree $ E_{\mathcal{P}}(x) $ and $ E_{\mathcal{C}}(x) $ in vim. | 50 |

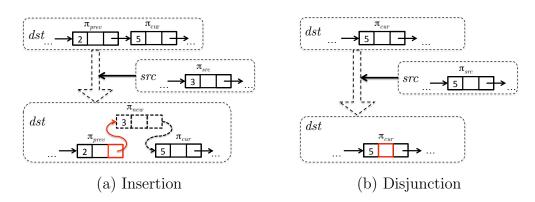

| 4.4 | Two lock-free atomic operations for merging an element. $\ldots$ .                                  | 55 |

| 4.5 | Comparing individual and group propagation schemes                                                  | 61 |

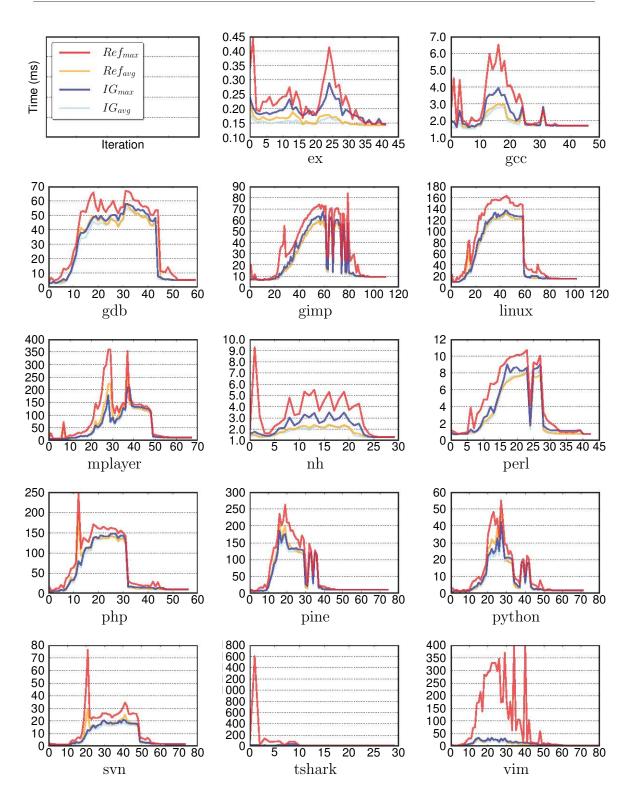

| 4.6 | Effectiveness of load balancing achieved by the two proposed schemes.                               | 71 |

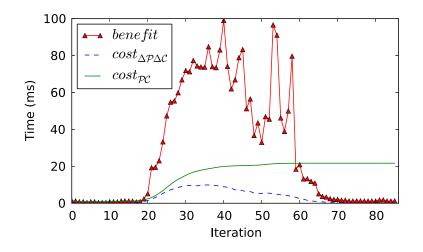

| 5.1 | A cost-benefit analysis for the ${\tt svn}$ benchmark                                               | 85 |

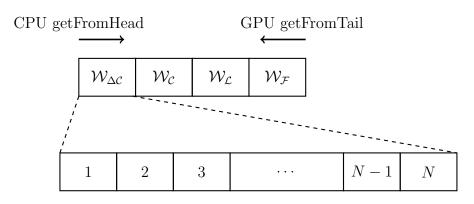

| 5.2 | The shared worklist $\mathcal{W}$ used in Algorithm 11                                              | 87 |

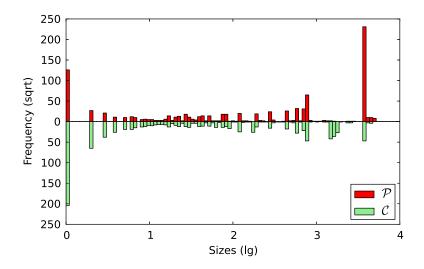

| 5.3 | Sizes of points-to and copy edges for svn                       | 88 |

|-----|-----------------------------------------------------------------|----|

| 5.4 | The shared worklist $\mathcal{W}$ used in Algorithm 12          | 90 |

| 5.5 | Speedups of our parallel Andersen's analysis and their CPU-only |    |

|     | and GPU-only versions.                                          | 96 |

# List of Tables

| 2.1 | Initialisation: mapping program statements to constraint edges | 10  |

|-----|----------------------------------------------------------------|-----|

| 2.2 | Constraint resolution: graph-rewriting rules.                  | 11  |

| 3.1 | Benchmark information.                                         | 38  |

| 3.2 | Statistics for data sharing                                    | 42  |

| 3.3 | Statistics for query scheduling                                | 45  |

| 4.1 | Benchmark statistics: sizes of initial constraint graphs       | 66  |

| 4.2 | Kernel configurations.                                         | 68  |

| 4.3 | Analysis times and speedups.                                   | 69  |

| 4.4 | Effectiveness of adaptive group propagation                    | 73  |

| 4.5 | The speedups of $Ref$ , $IG$ and $CPU$ -16 over the baseline   | 74  |

| 5.1 | Constraint resolution: graph-rewriting rules.                  | 83  |

| 5.2 | Benchmark suite: sizes of initial constraint graphs            | 93  |

| 5.3 | Analysis of our CPU-GPU solution (including its key method em- |     |

|     | ployed)                                                        | 97  |

| 5.4 | Analysis of our CPU-GPU solution (including its key method and |     |

|     | optimisations employed)                                        | 99  |

| 6.1 | Comparing different parallel pointer analysis                  | 103 |

# List of Algorithms

| 1  | Sequential Andersen's Analysis.                                                                     | 12 |

|----|-----------------------------------------------------------------------------------------------------|----|

| 2  | CFL-reachability-based pointer analysis                                                             | 24 |

| 3  | REACHABLENODES with data sharing.                                                                   | 31 |

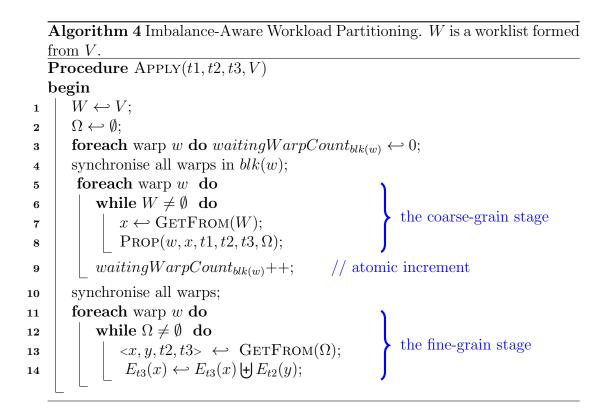

| 4  | Imbalance-Aware Workload Partitioning.                                                              | 52 |

| 5  | Imbalance-Aware Propagation                                                                         | 53 |

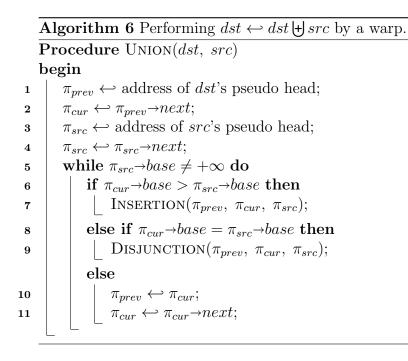

| 6  | Performing $dst \leftarrow dst \biguplus src$ by a warp                                             | 57 |

| 7  | Atomic insertion of one element from $src$ into $dst$                                               | 57 |

| 8  | Atomic disjunction of an element from $src$ with another in $dst.$ $\ .$ .                          | 58 |

| 9  | Implementing $\pi_{src} \leftrightarrow \pi_{src} \rightarrow next$ for a virtual sparse bit vector | 64 |

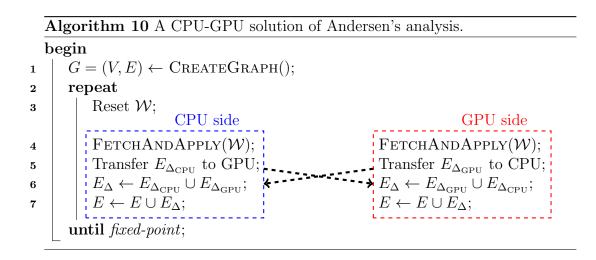

| 10 | A CPU-GPU solution of Andersen's analysis                                                           | 81 |

| 11 | A naive workload distribution scheme.                                                               | 87 |

| 12 | A DI-based dynamic workload distribution                                                            | 90 |

## Chapter 1

# Introduction

Pointers are an essential feature of mainstream programming languages (e.g., C, C++, Java). Pointer analysis, which determines statically what a pointer may point to at runtime, is a fundamental analysis for understanding the behaviours of a program. This analysis provides points-to information, which enables many applications such as compiler optimisation [7], bug detection [9, 66] and security analysis [6]. With a rich literature, it has been one of the most popular research areas in computer science [18]. Depending on how points-to information is provided, two types of pointer analyses have been studied for long: (1) whole-program analysis, which computes points-to information for all variables in the program; and (2) demand-driven analysis, which determines the points-to information only for the variables that are requested by clients. Both types of analyses are important, with the whole-program analysis incorporated in production-quality compilers for all kinds of analysis and transformation, and the demand-driven analysis laying foundations for clients such as software debugging [43, 45, 48] and alias disambiguation [52].

The main problem with developing a practical pointer analysis tool is enhanc-

ing its efficiency while maintaining its precision. Great efforts have been made on making tradeoffs between precision and efficiency across several dimensions, including field-sensitivity (by matching field accesses) [37], context-sensitivity (by distinguishing calling contexts) [44, 45, 52, 60, 62, 68] and flow-sensitivity (by considering control flow) [15, 23, 57, 68]. Over the years, many performance improvements have been made, in the sequential setting, on accelerating both whole-program analysis [10, 11, 14, 34, 36, 38, 52] and demand-driven analysis [26, 42, 43, 45, 48, 65, 71]. However, precise pointer analysis is still costly when applied to large programs. In recent years, with the ubiquity of parallel platforms, including multicore CPUs [8, 29, 31, 33, 40] and GPUs [28, 32], boosting the performance of pointer analysis by exploring parallelisation techniques has become an increasingly popular research topic.

### 1.1 Challenges

Pointer analysis, which is essentially an irregular graph problem, is very challenging to parallelise efficiently on multicore CPUs, GPUs or heterogeneous CPU-GPU systems. Whole-program pointer analysis, which often comes in Andersen's inclusionbased style (by considering pointer assignments as subset constraints) [2], is a graph algorithm that makes extensive modifications to the underlying graph representing the program being analysed. Demand-driven pointer analysis, which is driven by queries from clients and founded on Context-Free Language (CFL) reachability [41], is a graph traversal problem with massive parallelism-inhibiting dependences.

CFL-reachability-based demand-driven pointer analysis has never been parallelised in the literature. Previous studies are focused on its sequential algorithm, by resorting to refinement [45, 48, 71], summarisation [43, 65], incrementalisation [26, 42], pre-analysis [64] and ad-hoc caching [45, 64]. On parallel platforms, however, it is crucial but difficult to avoid the redundant graph traversals both within and across the queries, in order to fully utilise the computational resources. The new points-to/alias information discovered in answering some queries during graph traversals is not directly available to other queries on the (read-only) graph representation of the program. For precise CFL-reachability-based analysis with field- and context-sensitivity, there are massive parallelism-inhibiting dependences as well. These dependences are introduced into its various analysis stages since processing a query involves matching calling contexts and handling heap accesses throughout the program.

Andersen's inclusion-based pointer analysis is promising yet difficult to parallelise on GPUs. In recent years, several parallel implementations of Andersen's analysis have been introduced to enhance its performance on multicore CPUs [29, 40] and GPUs [28]. The latter platform is chosen for such an analysis in this thesis since a GPU is possible to deliver better performance than a multicore CPU at a lower price [28]. However, existing work [28] is still inefficient due to extensive modifications to the underlying graph representing the program being analysed. These modifications are highly irregular, input-dependent and statically unpredictable. The skewed and dynamically-changing distribution of edges in a graph leads to a highly imbalanced workload distribution across its nodes, where the higher-degree nodes induce larger processing tasks. As a result, GPUs can perform poorly when their computational resources are severely underutilised.

It is another challenge to parallelise Andersen's pointer analysis on a heterogeneous CPU-GPU system. The obstacle lies in making full use of computational resources of both CPU and GPU. It is important to notice that CPUs behave better for some applications while GPUs prevail for others, indicating that the relative suitability of CPUs or GPUs for applications varies depending on their workload characteristics. The challenges in exploring a heterogeneous CPU-GPU system are two-fold. First, the workload distribution between the CPU and GPU must be balanced with negligible runtime overhead. This is non-trivial since different programs give rise to different graphs to be analysed and the structure of a graph changes unpredictably during the analysis. Second, the CPU-GPU communication must be minimised in terms of the amount of data exchanged and the degree of overlap with computation on CPU and GPU. This is also non-trivial because the graphs being analysed are dynamically changing, making it hard to extract the "right" amount of information to communicate between the CPU and GPU with reasonable overhead.

### **1.2** Our Approaches

In order to address the above challenges, this thesis proposes a series of parallelisation techniques to speed up both CFL-reachability-based pointer analysis and Andersen's inclusion-based pointer analysis.

Reducing Unnecessary Graph Traversals for CFL-Reachability-based Analysis Redundant graph traversals can be the major cost to CFL-reachabilitybased pointer analysis. We present two novel techniques, *data sharing* and *query scheduling*, to reduce redundant graph traversals. With data sharing, the original graph traversal problem is recast into a graph rewriting problem. By adding new edges to the graph representation to shortcut the paths traversed in a query, retraversing (redundantly) the same paths can be avoided by taking their short-cuts instead when handling subsequent queries. With query scheduling, the queries to be issued (in batch mode) are prioritised according to their statically estimated dependences so that more redundant graph traversals can be further reduced.

Balancing Workload for Whole Program Analysis on GPU Load imbalance causes underutilisation in GPU cores and results in severe performance issues. We propose an imbalance-aware workload partitioning scheme that divides the workload dynamically among the concurrent warps, initially in a warp-centric manner as in [28] (during its coarse-grain stage) but later switches to a task-poolbased model (during its fine-grain stage) as soon as a workload imbalance is detected. The coarse-grain stage makes use of a so-called pull-based method so that addition of edges can be performed in a synchronisation-free manner. This stage is efficient as long as workload is balanced and the computational resources on the GPU are fully utilised. The fine-grain stage tackles situations where load imbalance is detected by further decomposing long tasks. When propagating edge sets for nodes during the analysis, there can be redundant traversals and computations. We propose an adaptive group propagation scheme to reduce unnecessary graph traversals and edge set propagations. This scheme also facilitates load balancing when redundant traversals and propagations involving high-degree nodes are reduced.

Workload Distribution and Communication Management for Heterogeneous Systems CPUs and GPUs behave in different manners in processing workloads with distinct characteristics. We prioritise the distribution of different types of graph-rewriting rules (i.e., workloads) to CPU or GPU according to the degrees of the processing unit's suitability for processing them. In this way, both CPU and GPU are more likely to get the workload which they are able to process more efficiently. With separate memory spaces, communication can be a major cost for the analysis. We adopt difference propagation to transfer new points-to information between CPU and GPU and overlap this process with some computations.

### **1.3** Contributions

**Demand-Driven Pointer Analysis on Multicore CPUs** This is the first parallel implementation of context- and field-sensitive pointer analysis with CFLreachability for Java programs. This implementation uses a data sharing scheme to reduce redundant graph traversals (in all query-processing threads) by graph rewriting, and a query scheduling scheme to eliminate unnecessary traversals further, by prioritising queries according to their statically estimated dependences. Evaluated with a set of 20 Java benchmarks, this parallel solution achieves an average speedup of 16.2X over a state-of-the-art sequential implementation with 16 threads on 16 CPU cores.

Efficient Whole-Program Pointer Analysis on GPU While [28] focuses on producing the first-ever GPU implementation of Andersen's analysis via graphrewriting, this thesis leverages that implementation but addresses its load balancing problem, thereby accelerating this analysis significantly further as well as providing insights for parallelising other graph algorithms that also make modifications to their input graphs. This is achieved by an imbalance-aware workload partitioning scheme that includes a warp-centric stage (coarse-grain) and a taskpool-based stage (fine-grain), and an adaptive group propagation scheme to avoid some redundant graph traversals and computations. The evaluation in terms of 14 C benchmarks used in prior work shows that this parallel implementation achieves a significant speedup of 46% on average over the state-of-the-art GPU implementation [28]. Whole-Program Pointer Analysis on Heterogeneous CPU-GPU Systems This is the first implementation of Andersen's analysis on a heterogeneous CPU-GPU system. It takes advantage of a previous formulation of this analysis in terms of graph-rewriting rules [28] to ensure that all rule applications on CPU and GPU are synchronisation-free. It proposes a dynamic workload distribution scheme that dispatches a particular type of workload to the processor, CPU or GPU, that is better suited for the workload. It employs a difference propagation scheme for transferring new points-to information discovered between CPU and GPU to reduce communication cost. The evaluation using seven C benchmarks shows that this CPU-GPU solution outperforms (on average) (1) the CPU-only solution by 50.6%, (2) the GPU-only solution by 78.5%, and (3) an oracle that behaves as the faster of (1) and (2) on every benchmark by 34.6%, where (1) and (2) are variants of state-of-the-art implementations introduced in [28].

### 1.4 Thesis Organisation

The rest of this thesis is organised as follows:

Chapter 2 provides the general background of pointer analysis. As the targets of our parallel solutions in this thesis, Andersen's inclusion-based pointer analysis and CFL-reachability-based pointer analysis are introduced in details.

Chapter 3 presents the first parallel solution to CFL-reachability-based pointer analysis. With a data sharing scheme and a query scheduling scheme, it successfully reduces redundant traversals in the analysis.

Chapter 4 describes an efficient GPU solution to Andersen's inclusion-based pointer analysis, which is based on an state-of-the-art GPU implementation and improves its performance with an imbalance-aware workload balancing scheme and a group propagation scheme.

Chapter 5 introduces the first parallel solution to Andersen's inclusion-based pointer analysis on a heterogeneous CPU-GPU system. It presents techniques for matching suitable workload to CPU or GPU and minimising communications between them.

Chapter 6 concludes the thesis and discusses future work.

# Chapter 2

## Background

This thesis focuses on both whole-program and demand-driven analyses, given their importance in program analysis and software engineering. We provide some preliminaries on these two types of pointer analyses in Sections 2.1 and 2.2 respectively, before introducing our parallel solutions to them.

## 2.1 Whole-Program Pointer Analysis

Due to its scalability, Andersen's pointer analysis, an inclusion-based flow- and context-insensitive whole-program analysis, has been adopted by production compilers such as Open64, LLVM and GCC, and also has become the focus of this thesis. Section 2.1.1 introduces this analysis with its sequential algorithm and Section 2.1.2 describes its state-of-the-art parallel implementation on a GPU.

### 2.1.1 Andersen's Inclusion-based Pointer Analysis

Andersen's analysis for a program is often formulated by solving a set-constraint problem over a directed graph, G = (V, E), called a *constraint graph*. We first discuss its initialisation and constraint resolution, then present its algorithm, and finally, illustrate it with an example.

**Initialisation** Given a C program, its constraint graph G = (V, E) is created with its node set V being the variables in the program and its edge set E representing five different types of pointer-manipulating statements in the program, as shown in Table 2.1. At this stage, there is one edge for every such a statement in the program.

| Name                                 | Statement | Edge                               |

|--------------------------------------|-----------|------------------------------------|

| points-to $(\mathcal{P})$            | x = & y   | $x \xrightarrow{\mathcal{P}} y$    |

| $\operatorname{copy}\ (\mathcal{C})$ | x = y     | $x \xrightarrow{\mathcal{C}} y$    |

| load $(\mathcal{L})$                 | x = *y    | $x \xrightarrow{\mathcal{L}} y$    |

| store $(\mathcal{S})$                | *x = y    | $x \xrightarrow{\mathcal{S}} y$    |

| offset $(\mathcal{F})$               | x = y + o | $x \xrightarrow[o]{\mathcal{F}} y$ |

Table 2.1: Initialisation: mapping program statements to constraint edges.

For example,  $x \xrightarrow{\mathcal{P}} y$  represents a points-to (i.e.,  $\mathcal{P}$ ) edge directing out of node x into node y. The four other types of edges are understood similarly. Offset edges are introduced for enabling field-sensitivity so that a field of a struct is treated as a separate variable. However, an array is usually analysed as a whole (with its elements collapsed).

We use  $E_t$  to represent a subset of E containing all the edges of type t. For example,  $E_{\mathcal{P}}$  is the set of all  $\mathcal{P}$  edges in E and  $E_{\mathcal{C}}$  is the set of all  $\mathcal{C}$  edges in E. This notation will be used heavily in many algorithms presented later in the thesis.

**Constraint Resolution** Once the constraint graph G = (V, E) for a program is initialised, we can start discovering new points-to information in the program

during a so-called constraint resolution process. V (as the set of program variables) will obviously stay unchanged. However, E may grow as new points-to ( $\mathcal{P}$ ) and copy ( $\mathcal{C}$ ) edges are added by applying graph-rewriting rules iteratively until a fixedpoint is reached. Note that the load ( $\mathcal{L}$ ), store ( $\mathcal{S}$ ) and offset ( $\mathcal{F}$ ) edges will remain the same.

Propagating the points-to information initially available in G along its edges iteratively is time-consuming. In practice, we can avoid some redundant computations by propagating only the new information discovered to where it is needed. This can be achieved with *difference propagation* [11, 36, 46], in which the newly added  $\delta \mathcal{P}$  and  $\delta \mathcal{C}$  edges to G in one iteration are distinguished from the  $\mathcal{P}$  and  $\mathcal{C}$ edges available before this iteration.

| Rule                 | Semantics                                                                                                                           |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| $R_{copy}(x)$        | $x \xrightarrow{\mathcal{C}} y \land y \xrightarrow{\Delta \mathcal{P}} z \Rightarrow x \xrightarrow{\delta \mathcal{P}} z$         |

| $R_{load}(x)$        | $x \xrightarrow{\mathcal{L}} y \land y \xrightarrow{\Delta \mathcal{P}} z \Rightarrow x \xrightarrow{\delta \mathcal{C}} z$         |

| $R_{store}(x)$       | $x \xrightarrow{\Delta \mathcal{P}^{-1}} y \land y \xrightarrow{\mathcal{S}} z \Rightarrow x \xrightarrow{\delta \mathcal{C}} z$    |

| $R_{\delta copy}(x)$ | $x \xrightarrow{\delta \mathcal{C}} y \land y \xrightarrow{\mathcal{P}} z \Rightarrow x \xrightarrow{\delta \mathcal{P}} z$         |

| $R_{offset}(x)$      | $x \xrightarrow{\mathcal{F}}_{o} y \land y \xrightarrow{\Delta \mathcal{P}} z \Rightarrow x \xrightarrow{\delta \mathcal{P}} z + o$ |

Table 2.2: Constraint resolution: graph-rewriting rules.

Table 2.2 lists five types of graph-rewriting rules used in constraint resolution. Note that there are two types of newly added points-to edges,  $\Delta \mathcal{P}$  and  $\delta \mathcal{P}$ . For each iteration, the  $\Delta \mathcal{P}$  edges in the premise signify the new points-to edges generated in the previous iteration and being used in the current iteration, and the  $\delta \mathcal{P}$  edges in the conclusion represent the new points-to edges being produced in the current iteration. For new copy edges, only one version, i.e.,  $\delta \mathcal{C}$  is maintained, because they are produced by  $R_{load}$  and  $R_{store}$  and used only later by  $R_{\delta copy}$  in the same iteration (by Algorithm 1).

```

Algorithm 1 Sequential Andersen's Analysis.

Procedure ANDERSEN()

begin

G = (V, E) \leftrightarrow \text{CREATEGRAPH}();

1

\mathbf{2}

repeat

APPLY(\mathcal{C}, \Delta \mathcal{P}, \delta \mathcal{P}, V);

3

APPLY(\mathcal{L}, \Delta \mathcal{P}, \delta \mathcal{C}, V);

\mathbf{4}

APPLY(\Delta \mathcal{P}^{-1}, \mathcal{S}, \delta \mathcal{C}, V);

\mathbf{5}

APPLY(\delta C, \mathcal{P}, \delta \mathcal{P}, V);

6

APPLYOFFSET(\mathcal{F}, \Delta \mathcal{P}, \delta \mathcal{P}, V);

7

E_{\Delta \mathcal{P}} \leftrightarrow E_{\delta \mathcal{P}} \setminus E_{\mathcal{P}}; \quad // \text{ update}

8

E_{\mathcal{P}} \xleftarrow{} E_{\mathcal{P}} \cup E_{\delta \mathcal{P}}; \quad // \text{ update}

9

E_{\mathcal{C}} \leftarrow E_{\mathcal{C}} \cup E_{\delta \mathcal{C}}; \quad // \text{ update}

10

until fixed-point;

Procedure APPLY(t1, t2, t3, V)

begin

foreach x \in V do

11

foreach y \in E_{t1}(x) do

12

E_{t3}(x) \leftarrow E_{t3}(x) \cup E_{t2}(y);

\mathbf{13}

Procedure APPLYOFFSET(t1, t2, t3, V)

begin

foreach x \in V do

\mathbf{14}

foreach y \in E_{t1}(x) do

15

Let this offset edge (x, y) be x \xrightarrow[]{\mathcal{F}}{} y;

16

E_{t3}(x) \longleftrightarrow E_{t3}(x) \cup \{z + o \mid z \in \overset{o}{E}_{t2}(y)\};

\mathbf{17}

```

**Algorithm** Algorithm 1 gives a sequential procedure for performing Andersen's analysis. Given a program, CREATEGRAPH is called to initialise its constraint graph G = (V, E) as discussed earlier and the graph-rewriting rules in Table 2.2 are applied in sequence until a fixed-point is reached as discussed above. Recall that we use  $E_t$  to represent a subset of E containing all the edges of type t. In this algorithm, for example,  $E_{\mathcal{P}}$  is the set of all  $\mathcal{P}$  edges in E and  $E_{t1}(x)$  denotes the set of edges of type t1 associated with the node x being processed.

For each rule of the form of  $x \xrightarrow{t1} y \land y \xrightarrow{t2} z \Rightarrow x \xrightarrow{t3} z$  in Table 2.2, we call APPLY or APPLYOFFSET, whichever is appropriate, to apply it to every node x in the program to discover any new edges of type t3 for node x. At the end of each iteration (lines 8 – 10), the  $\Delta \mathcal{P}$ ,  $\mathcal{P}$  and  $\mathcal{C}$  edges are updated to prepare for the next iteration.

**Example** Let us apply Algorithm 1 to a program given in Figure 2.1(a). The analysis starts with the constraint graph created by CREATEGRAPH in Figure 2.1(b). This graph is then modified into the ones in Figures 2.1(c) – 2.1(e) during iterations 1 – 3, respectively. A fixed-point is reached at the end of iteration 3. In each iteration, the newly discovered edges are highlighted in dashed arrows. Figure 2.1(f) illustrates the difference propagation in terms of the  $\Delta \mathcal{P}$ ,  $\delta \mathcal{P}$  and  $\delta \mathcal{C}$  edges during each iteration.

In the first iteration,  $E_{\Delta \mathcal{P}}$  contains  $x \xrightarrow{\Delta \mathcal{P}} a$  and  $a \xrightarrow{\Delta \mathcal{P}} o$ , which were added during initialisation.  $\mathsf{R}_{\mathsf{copy}}$  is applied to y, resulting in  $y \xrightarrow{\delta \mathcal{P}} a$  added. At this stage, none of the rules is applicable. Then  $y \xrightarrow{\delta \mathcal{P}} a$  is included to the  $\Delta \mathcal{P}$  and  $\mathcal{P}$  edges (lines 8 – 9).

In the second iteration, applying  $\mathsf{R}_{\mathsf{load}}$  to b causes  $b \xrightarrow{\delta C} a$  to be discovered. Then  $\mathsf{R}_{\delta\mathsf{copy}}$  is applied to b with  $b \xrightarrow{\delta \mathcal{P}} o$  added. Next,  $\mathsf{R}_{\mathsf{offset}}$  is applied to z, with  $z \xrightarrow{\delta \mathcal{P}} a + 2$  discovered. Finally, the  $\Delta \mathcal{P}$ ,  $\mathcal{P}$  and  $\mathcal{C}$  edges are updated accordingly (lines 8 – 10).

In the last iteration,  $\mathsf{R}_{\mathsf{store}}$  is applied to a + 2, giving rise to  $a + 2 \xrightarrow{\delta \mathcal{C}} b$ , and resulting in  $a + 2 \xrightarrow{\delta \mathcal{P}} o$  to be discovered by  $\mathsf{R}_{\delta \mathsf{copy}}$ . These two new edges become  $a + 2 \xrightarrow{\mathcal{C}} b$  and  $a + 2 \xrightarrow{\mathcal{P}} o$  (as  $a + 2 \xrightarrow{\Delta \mathcal{P}} o$  initially due to difference propagation) at the end of this iteration. A fixed-point is then reached since no more rules can be applied.

| a = & o                                                                                                                                 |                            | Iteration 1       | Iteration 2                                           | Iteration 3                                         |  |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------|-------------------------------------------------------|-----------------------------------------------------|--|

| x = &a                                                                                                                                  | $\Delta \mathcal{P}$       | $x \to a$         | $y \to a$                                             | $b \rightarrow o$                                   |  |

| y = x                                                                                                                                   | $\Delta P$                 | $a \rightarrow o$ |                                                       | $z \to a+2$                                         |  |

| b = *y $z = y + 2$                                                                                                                      | $\delta \mathcal{P}$       | $y \rightarrow a$ | $ \begin{array}{c} b \to o \\ z \to a+2 \end{array} $ | $a + 2 \rightarrow o$                               |  |

| *z = b                                                                                                                                  | $\delta C$                 |                   | $b \rightarrow a$                                     | $a+2 \rightarrow b$                                 |  |

| (a) Program code                                                                                                                        | (f) Difference propagation |                   |                                                       |                                                     |  |

| $ \begin{array}{c} x \\ x \\ \hline \\  \\  \\  \\  \\  \\  \\  \\  \\  \\  \\  \\  \\  $                                               | (a+2)                      | (                 | x  C  y $P  P  L$ $a  b$ $b$                          | $\mathcal{F}$ z z z z z z z z z z z z z z z z z z z |  |

| (b) Initialisation                                                                                                                      |                            |                   | (c) Iteration 1                                       |                                                     |  |

| $x \leftarrow C \qquad y \leftarrow F$ $p \qquad p \qquad L \qquad S$ $a \leftarrow C \qquad b \qquad b$ $p \qquad p \qquad c \qquad b$ | $\mathcal{P}$              | (                 | x  C  y $p  p  L$ $a  C  b$ $p  p  p$                 | F<br>S<br>P<br>C<br>a+2                             |  |

| (d) Iteration 2                                                                                                                         |                            |                   | (e) Iteration 3                                       |                                                     |  |

Figure 2.1: An example illustrating Andersen's analysis. The initial graph is the one in (b), where a is a variable representing the address of a struct and the address of its first field, and a+2 denotes its third field. Note that for illustration purposes, this graph only shows variables directly relevant to the example. For instance, the second field a + 1, which never occurs in the program, is not shown in the graph. The new edges added in an iteration are shown in dashed arrows. The fixed-point is reached after iteration 3.

### 2.1.2 State-of-the-Art

We explain the first GPU implementation of Andersen's analysis [28]. We start by reviewing the GPU architecture and the CUDA programming model. We then describe a sparse bit vector representation that is often used in pointer analysis but adapted for this GPU implementation. Finally, we examine its workload partitioning scheme used, together with its inherent load balancing issues.

**GPU Architecture** We use an NVIDIA TESLA K20c GPU in our evaluation, but the general techniques introduced in this thesis are not tied to any specific GPU architecture. This GPU consists of 13 streaming multiprocessors (SMXs), each containing 192 cores, giving rise to 2496 GPU cores in total. In addition, the GPU has a global memory (i.e., off-chip memory) bandwidth of 208GB/s. However, each GPU core clocks at only 0.71GHz and the global memory access latency reaches 400 – 800 cycles. This suggests that a GPU is well suited for regular, balanced workloads with abundant data parallelism when its massive number of cores and high memory bandwidth are fully utilised. However, a GPU can perform poorly when its cores and memory bandwidth are underutilised, which usually happens for irregular, imbalanced workloads.

In the CUDA programming model, threads are organised in *thread blocks*. All the threads in one block are executed on one SMX, while one SMX can have multiple concurrent blocks. One block has several *warps*, each containing 32 parallel threads.

In the case of imbalanced workloads, the computational resources in a GPU may be underutilised in two scenarios. First, all the threads in a warp execute the same instruction concurrently in an SIMD (Single Instruction Multiple Data) manner, but can be severely serialised on divergent control flows (known as *intra-warp divergence*). Second, all the warps in a thread block running on an SMX are

time-shared to hide memory latency, but a few long-running warps may lead to underutilisation of its cores (known as *inter-warp load imbalance*).

**Sparse Bit Vectors** A sparse bit vector, implemented as a singly linked list, represents a set of integers. Each element in the list consists of three fields: *bits* (several words) represents whether the corresponding integer belongs to the set, *base* (1 word) indicates the range of integers that is represented in this element, and *next* (1 word) points to the next element. The prior work in pointer analysis [14] has demonstrated that sparse bit vectors are compact for representing constraint graphs while facilitating efficient applications of graph-rewriting rules. In their GPU implementation of Andersen's analysis, [28] used 32-word elements, where the *bits* field spans 30 words (960 bits). This helps mitigate intra-warp divergence, since all 32 threads in a warp can perform operations (e.g., a coalesced global memory access [61, 70] and a bitwise *OR* for  $\cup$ ) on the 32 words in parallel.

In a constraint graph G = (V, E), all the variables, i.e., nodes in V are mapped to consecutive integers, starting from 0. Given a node x, all its (outgoing) edges in  $E_t(x)$  of type t are stored in a separate list. Let us consider an example when xhas two outgoing points-to edges  $x \xrightarrow{\mathcal{P}} y$  and  $x \xrightarrow{\mathcal{P}} z$ , of type t, where y and z are identified by integers 958 and 1920, respectively. The sparse representation of x's (outgoing) edges of type t is illustrated in Figure 2.2. It is a linked list with two elements. The first element's base is 0 and the 958<sup>th</sup> bit in bits is 1. So it contains the integer 960  $\times$  0 + 958 = 958, i.e., y. The second element's base is 2 and the 0<sup>th</sup> bit in bits is 1. As a result, it contains z, identified by integer 960  $\times$  2 + 0 = 1920. Note that a sparse bit vector is implemented as a singly sorted linked list, with its elements sorted in increasing order of their bases. In addition, different elements on the same list will always have different bases.

With sparse bit vectors, the set union operation in line 13 in Algorithm 1 can

| base | bits | next | base                          | bits | next |

|------|------|------|-------------------------------|------|------|

| 0000 | 0100 |      | $\longrightarrow 0 \dots 010$ | 0001 | NULL |

Figure 2.2: Sparse bit vector representing {958, 1920}.

be implemented as follows. If  $z \in E_{t2}(y)$  has a *base* that is not available in  $E_{t3}(x)$ , then z is inserted into  $E_{t3}(x)$  wherever appropriate. Otherwise, the *bits* field of z is merged (via a bitwise OR) with the *bits* part of the element in  $E_{t3}(x)$  that shares the same *base*. The set union in line 17 in Algorithm 1 is handled similarly.

Warp-Centric Workload Partitioning In the GPU implementation introduced in [28], Andersen's analysis (given in Algorithm 1) is parallelised in a warpcentric manner [19]. During each iteration (of its **repeat** loop), the five types of rules (in lines 3 - 7) are applied sequentially, with synchronisation enforced between every two consecutive rule applications. However, each rule is applied in parallel to all the nodes in the program. So the **foreach** loops in lines 11 and 14 are essentially DOALL loops. When applied to every individual node x (lines 12 - 13 in APPLY and lines 15 - 17 in APPLYOFFSET), each rule is executed by one warp,  $warp_x$ , in a warp-centric manner. As  $warp_x$  will add new edges only at node x and such new edges are never used by the other concurrent warps (due to difference propagation), different applications of the same rule at different nodes do not require any synchronisation.

To apply  $\mathsf{R}_{\mathsf{store}}$ , the pointed-by  $(\Delta \mathcal{P}^{-1})$  edges are required. For space considerations,  $E_{\Delta \mathcal{P}^{-1}}$  is not explicitly stored as it can be obtained from its inverse  $E_{\Delta \mathcal{P}}$ efficiently. For this rule, the set  $\Delta \mathcal{P}$  involved is small since the number of store edges is relatively small and remains unchanged during the analysis. In addition, pairs (x, y) are extracted from  $E_{\Delta \mathcal{P}}$  only when both y has some outgoing store edges and  $y \xrightarrow{\mathcal{P}} x$  holds. All pairs with the same first component are assigned to the same warp.

For this particular GPU implementation, intra-warp divergence is mitigated by letting the 32 threads in a warp run in parallel on a 32-word element in a sparse bit vector, with one word per thread. However, this simple warp-centric approach suffers from underutilisation of warp resources, since some warps processing lowdegree nodes finish much earlier than those processing high-degree nodes. Several heuristics are employed in [28] to alleviate this inter-warp imbalance problem. First, due to the absence of read-write conflicts between  $R_{copy}(x)$  (line 3) and  $R_{load}(x)$ (line 4), no synchronisation is necessary in between. Second,  $R_{\delta copy}(x)$  (line 6) is combined with both  $R_{load}(x)$  and  $R_{store}(x)$  (so that  $R_{copy}(x)$  is applied immediately after each of these two rules at a node). Finally,  $R_{store}(x)$  is applied in a blockrather than warp-centric manner so that a node is processed by all warps in a thread block. Despite these heuristics, the GPU implementation [28] still suffers from extremely imbalanced workloads for many programs.

## 2.2 Demand-Driven Pointer Analysis

Demand-driven pointer analysis is founded on CFL-reachability [41] [26, 42, 43, 45, 48, 65, 71]. By computing the points-to information of some variables (instead of all variables as in whole-program Andersen's analysis), demand-driven analysis can be performed both context- and field-sensitively to achieve better precision more scalably than Andersen's analysis, especially for Java programs. Section 2.2.1 describes the intermediate representation used for analysing Java programs. Section 2.2.2 reviews the standard formulation of pointer analysis in terms of CFL-reachability.

#### 2.2.1 Program Representation

We focus on Java although this thesis applies equally well to C [71]. A Java program is represented as a *Pointer Assignment Graph (PAG)*, as defined in Figure 2.3.

| n | :=                        | $v \mid o$                                                 | Node              |

|---|---------------------------|------------------------------------------------------------|-------------------|

| v | :=                        | $l \mid g$                                                 | Variable          |

| e | :=                        | $l_1 \xleftarrow{new} o$                                   | Allocation        |

|   |                           | $l_1 \xleftarrow{assign^l} l_2$                            | Local Assignment  |

|   |                           | $g \xleftarrow{assign^g} v \mid v \xleftarrow{assign^g} g$ | Global Assignment |

|   |                           | $l_1 \xleftarrow{Id(f)} l_2$                               | Load              |

|   |                           | $l_1 \xleftarrow{st(f)} l_2$                               | Store             |

|   |                           | $l_1 \xleftarrow{param_i} l_2$                             | Parameter         |

|   |                           | $l_1 \xleftarrow{ret_i} l_2$                               | Return            |

|   | $l \in Loca$ $i \in Call$ | 0                                                          | $o \in Object$    |

Figure 2.3: Syntax of PAG (pointer assignment graph).

A node *n* represents a variable *v* or an object *o* in the program, where *v* can be local (*l*) or global (*g*). An edge *e* represents a statement in the program oriented in the direction of its value flow. An edge connects only to local variables ( $l_1$  and/or  $l_2$ ) unless it represents an assignment involving at least one global variable (**assign**<sup>*g*</sup>). Let us look at the seven types of edges in detail.  $l_1 \xleftarrow{\mathsf{new}} o$  captures the flow of object *o* to variable  $l_1$ , indicating that  $l_1$  points directly to *o*.  $l_1 \xleftarrow{\mathsf{assign}^l} l_2$  represents a local assignment ( $l_1 = l_2$ ). A global assignment is similar except that one or both variables at its two sides are static variables in a class (i.e. *g*).  $l_1 \xleftarrow{\mathsf{ld}(f)} l_2$  represents a load of the form  $l_1 = l_2 \cdot f$  and  $l_1 \xleftarrow{\mathsf{st}(f)} l_2$  represents a store of the form  $l_1 \cdot f = l_2$ .  $l_1 \xleftarrow{\mathsf{param}_i} l_2$  models parameter passing, where  $l_2$  is an actual parameter and  $l_1$  is its corresponding formal parameter, at call site *i*. Similarly,  $l_1 \xleftarrow{\mathsf{ret}_i} l_2$  indicates an assignment of the return value in  $l_2$  to  $l_1$  at call site *i*.

Figure 2.4 gives an illustrating example and its PAG representation. Note that  $o_i$  denotes the object created at the allocation site in line *i* and  $v_m$  represents variable *v* declared in method *m*. Loads and stores to array elements are modeled by collapsing all elements into a special field, denoted **arr**.

#### 2.2.2 CFL-Reachability-based Pointer Analysis

CFL-reachability [41] is an extension of traditional graph reachability. Let G be a directed graph with edges labelled by letters over an alphabet  $\Sigma$  and L be a CFL over  $\Sigma$ . Each path p in G is composed of a string s(p) in  $\Sigma^*$ , formed by concatenating in order the labels of edges along p. A path p is an L-path iff  $s(p) \in L$ . Node x is L-reachable to y iff a path p from x to y exists, such that  $s(p) \in L$ . For a single-source reachability analysis, the worst-case time complexity is  $O(\Gamma^3 N^3)$ , where  $\Gamma$  is the size of a normalised grammar for L and N is the number of nodes in G.

**Field-Sensitivity** Let us start with a field-sensitive formulation without contextsensitivity. When calling contexts are ignored, there is no need to distinguish the four types of assignments,  $assign^{l}$ ,  $assign^{g}$ ,  $param_{i}$  and  $ret_{i}$ ; they are all identified as assignment edges of type assign.

For a PAG G with only new and assign edges, the CFL  $L_{\text{FT}}$  (FT for flows to) is a regular language, meaning that a variable v is  $L_{\text{FT}}$ -reachable from an object o in G iff o can flow to v. The rule for  $L_{\text{FT}}$  is defined as:

$$flowsTo \rightarrow \text{new}(assign)^*$$

(2.1)

with *flowsTo* as the start symbol. If *o flowsTo v*, then *v* is  $L_{\text{FT}}$ -reachable from *o*. For example, in Figure 2.4(a), since  $o_{15} \xrightarrow{\text{new}} v1_{\text{main}} \xrightarrow{\text{param}_{15}} \text{this}_{\text{Vector}}$ ,  $o_{15}$  flows

```

1\ {\tt class}\ {\tt Vector}\ {\tt }

12

t = this.elems;

2

Object[] elems;

13

return t[i];} // R t.arr

3

int count;

14 static void main(String[] args){

4

Vector(){

Vector v1 = new Vector();

15

5

count = 0;

16

String n1 = new String("N1");

t = new Object[MAXSIZE];

v1.add(n1);

6

17

this.elems = t;}

7

18

Object s1 = v1.get(0);

void add(Object e){

8

19

Vector v2 = new Vector();

t = this.elems;

9

20

Integer n2 = new Integer(1);

t[count++] = e;} // W t.arr

10

21

v2.add(n2);

Object get(int i){

Object s2 = v2.get(0);}}

11

22

```

(a) Java Code.

(b) PAG.

Figure 2.4: A Java example and its PAG.

to this<sub>Vector</sub>.

When field accesses are also handled, the CFL  $L_{\rm FS}$  (FS for field-sensitivity) is defined as follows:

$$flowsTo \rightarrow \text{new} ( \operatorname{assign} | \operatorname{st}(f) \ alias \operatorname{Id}(f))^{*}$$

$$alias \rightarrow \overline{flowsTo} \ flowsTo$$

$$\overline{flowsTo} \rightarrow ( \overline{\operatorname{assign}} | \overline{\operatorname{Id}(f)} \ alias \ \overline{\operatorname{st}(f)})^{*} \ \overline{\operatorname{new}}$$

$$(2.2)$$

The rule for *flowsTo* matches fields via st(f) *alias* Id(f), where st(f) and Id(f)are like a pair of parentheses [48]. For a pair of statements q.f = y (st(f)) and x = p.f (Id(f)), if p and q are aliases, then an object o that flows into y can flow first through this pair of parentheses (i.e. st(f) and Id(f)) and then into x. For example, in Figure 2.4(b), as  $o_{15} \xrightarrow{\text{new}} v1_{\text{main}} \xrightarrow{\text{param}_{15}} \text{this}_{\text{Vector}}$  and  $o_{15} \xrightarrow{\text{new}} v1_{\text{main}} \xrightarrow{\text{param}_{18}} \text{this}_{\text{get}}$ , we have this\_{Vector} alias this\_{\text{get}}. Thus  $o_6 \xrightarrow{\text{new}}$  $t_{\text{Vector}} \xrightarrow{\text{st(elems)}} \text{this}_{\text{Vector}}$  alias this\_{get}  $\xrightarrow{Id(elems)} t_{\text{get}}$ , indicating that  $o_6$  flows to  $t_{\text{get}}$ .

To allow the *alias* relation in the language,  $\overline{flowsTo}$  is introduced as the inverse of the *flowsTo* relation. For a *flowsTo*-path p, its corresponding  $\overline{flowsTo}$ -path  $\overline{p}$ can be obtained using inverse edges, and vice versa. For each edge  $x \stackrel{e}{\leftarrow} y$  in p, its inverse edge is  $y \stackrel{\overline{e}}{\leftarrow} x$  in  $\overline{p}$ . Therefore, o flowsTo x iff x flowsTo o, indicating that  $\overline{flowsTo}$  actually represents the points-to relation. To find the points-to set of a variable, we use the CFL given in (2.2) with  $\overline{flowsTo}$  as the start symbol.

**Context-Sensitivity** When context-sensitivity is considered,  $param_i$  and  $ret_i$  are treated as assign as before in  $L_{FS}$ . However,  $assign^l$  and  $assign^g$  are now distinguished.

A context-sensitive CFL requires  $param_i$  and  $ret_i$  to be matched, also in terms of balanced parentheses, by ruling out the unrealisable paths in a program [45]. The CFL  $R_{\rm CS}$  (CS for context-sensitivity) for capturing realisable paths is:

$$c \rightarrow entry_{i} c exit_{i} | c c | \epsilon$$

$$entry_{i} \rightarrow param_{i} | \overline{ret_{i}}$$

$$exit_{i} \rightarrow ret_{i} | \overline{param_{i}}$$

$$(2.3)$$

When traversing along a *flowsTo* path, after entering a method via  $param_i$  from call site *i*, a context-sensitive analysis requires exiting from that method back to call site *i*, via either ret<sub>i</sub> to continue its traversal along the same *flowsTo* path or  $\overline{param_i}$  to start a new search for a  $\overline{flowsTo}$  path. Traversing along a  $\overline{flowsTo}$  path is similar except that the direction of traversal is reversed. Consider Figure 2.4(a).  $s1_{main}$  is found to point to  $o_{16}$  as  $o_{16}$  reaches  $s1_{main}$  along a realisable path by first matching  $param_{17}$  and  $\overline{param_{17}}$  and then  $param_{18}$  and  $ret_{18}$ . However,  $s1_{main}$  does not point to  $o_{20}$  since  $o_{20}$  cannot reach  $s1_{main}$  along a realisable path.

Let  $L_{\rm PT}$  (PT for points-to) be the CFL for computing the points-to information of a variable field- and context-sensitively. Then  $L_{\rm PT}$  is defined in terms of (2.2) and (2.3):  $L_{\rm PT} = L_{\rm FS} \cap R_{\rm CS}$ , where  $\overline{flowsTo}$  is the start symbol.

Algorithm With CFL-reachability, a query that requests for a variable's pointsto information can be answered on-demand, according to Algorithm 2. This algorithm makes use of three variables: (1) E represents the edge set of the PAG of the program, (2) B is the (global) budget defined as the maximum number of steps that can be traversed by any query, with each node traversal being counted as one step [48], and (3) *steps* is query-local, representing the number of steps that has been traversed so far by a particular query.

Given a query (l, c), where l is a local variable and c is a context, POINTSTO computes the points-to set of l under c. It traverses the PAG with a work list Wmaintained for variables to be explored. *pts* is initialised with an empty set and W Algorithm 2 CFL-reachability-based pointer analysis, where POINTSTO computes  $\overline{flowsTo}$  and FLOWSTO is analogous to its inverse POINTSTO and thus omitted.

```

Global E; Const B; QueryLocal steps; // initially 0

Procedure POINTSTO(l, c)

begin

pts \leftarrow \emptyset;

1

W \leftarrow \{\langle l, c \rangle\};

\mathbf{2}

while W \neq \emptyset do

3

\langle x, c \rangle \leftarrow W.pop();

4

steps \leftarrow steps + 1;

5

if steps > B then OUTOFBUDGET(0);

6

for each x \xleftarrow{new} o \in E do pts \leftarrow pts \cup \{<o, c>\};

7

for

each x \xleftarrow{\text{assign}^l} y \in E do W.push(\langle y, c \rangle);

8

for each x \xleftarrow{\text{assign}^g} y \in E do W.push(\langle o, \epsilon \rangle);

9

foreach \langle y, c' \rangle \in \text{REACHABLENODES}(x, c) do

\mathbf{10}

W.push(\langle y, c' \rangle);

\mathbf{11}

foreach x \xleftarrow{\text{param}_i} y \in E do

12

if c = \epsilon or c.top() = i then

13

| W.push(\langle y, c.pop() \rangle); // \epsilon.pop() \equiv \epsilon

14

foreach x \xleftarrow{\mathsf{ret}_i} y \in E do W.push(\langle y, c.push(i) \rangle);

\mathbf{15}

return pts;

16

Procedure REACHABLENODES(x, c)

begin

rch \leftarrow \emptyset;

\mathbf{17}

for each x \xleftarrow{ld(f)} p \in E do

\mathbf{18}

foreach q \xleftarrow{st(f)} y \in E do

19

alias \leftarrow \emptyset:

\mathbf{20}

foreach \langle o, c' \rangle \in \text{POINTSTO}(p, c) do

\mathbf{21}

alias \leftarrow alias \cup FLOWSTO(o, c');

\mathbf{22}

foreach \langle q', c'' \rangle \in alias do

23

if q' = q then rch \leftarrow rch \cup \{\langle y, c'' \rangle\};

\mathbf{24}

return rch;

\mathbf{25}

Procedure OUTOFBUDGET(BDG)

begin

26 | exit();

```

with  $\langle l, c \rangle$  (lines 1 - 2). By default, *steps* for this query is initialised as 0. Each variable x with its context c, i.e.,  $\langle x, c \rangle$  obtained from W is processed as follows: *steps* is updated, triggering a call to OUTOFBUDGET if the remaining budget is 0 (lines 5 - 6), and the incoming edges of x are traversed according to (2.2) and (2.3) (lines 7 - 15).

Field-sensitivity is handled by REACHABLENODES(x, c), which searches for the reachable variables y to x in context c, due to heap accesses by matching the load (x = p.f) with every store (q.f = y), where p and q are aliases (lines 17 - 25). Both POINTSTO and FLOWSTO are called (recursively) to ensure that p and q are aliased base variables.

To handle context-sensitivity, the analysis stays in the same context c for  $\operatorname{assign}^{l}$ (line 8), clears c for  $\operatorname{assign}^{g}$  as global variables are treated context-insensitively (line 9), matches the context (c.top() = i) for  $\operatorname{param}_{i}$  but allows for partially balanced parentheses when  $c = \epsilon$  since a realizable path may not start and end in the same method (lines 12 - 14), and pushes call site i into context c for  $\operatorname{ret}_{i}$  (line 15).

# Chapter 3

# Demand-Driven Analysis on Multi-CPUs

In this chapter, we describe the first parallel implementation of demand-driven pointer analysis with CFL-reachability. We explore query level parallelism in the analysis and further accelerate it by reducing redundant graph traversals via a data sharing scheme and a query scheduling scheme. Our solution was previously proposed in [50]. Section 3.1 describes our parallel solution in terms of the data sharing and query scheduling schemes used. Section 3.2 evaluates our solution. Section 3.3 discusses the related work on demand-driven pointer analysis. Section 3.4 summarises this chapter.

# 3.1 Methodology

CFL-reachability-based pointer analysis is driven by queries issued by application clients. There are two main approaches to dividing work among threads, based on different levels of parallelism available: *intra-query* and *inter-query*.

To exploit intra-query parallelism, we need to partition and distribute the work

performed in computing the points-to set of a single query among different threads. Such parallelism is irregular and hard to achieve with the right granularity. In addition, considerable synchronisation overhead that may be incurred would likely offset the performance benefit achieved.

To exploit inter-query parallelism, we assign different queries to different threads, harnessing modern multicore processors. This makes it possible to obtain parallelism without incurring synchronisation overhead unduly. In addition, some clients may issue queries in batch mode for a program. For example, the points-to information may be requested for all variables in a method, a class, a package or even the entire program. This provides a further optimisation opportunity. The focus of this chapter is on exploiting inter-query parallelism.

#### 3.1.1 A Naive Parallelisation Strategy

A naive approach to exploiting inter-query parallelism is to maintain a lockprotected shared work list for queries and let each thread fetch queries (to process) from the work list until the work list is empty. While achieving some good speedups (over the sequential setting), this naive strategy is inefficient due to a large number of redundant graph traversals made. We propose two schemes to reduce such redundancies. Section 3.1.2 describes our data sharing scheme, while Section 3.1.3 explains our query scheduling scheme.

#### 3.1.2 Data Sharing

Given a program, we are motivated to add edges to its PAG to serve as shortcuts for some paths traversed in a query so that subsequent queries may take the shortcuts instead of re-traversing their associated paths (redundantly). The challenge here is to perform data sharing context- and field-sensitively. We first formulate data sharing in terms of graph rewriting, and then give an algorithm for realising data sharing in the CFL-reachability framework.

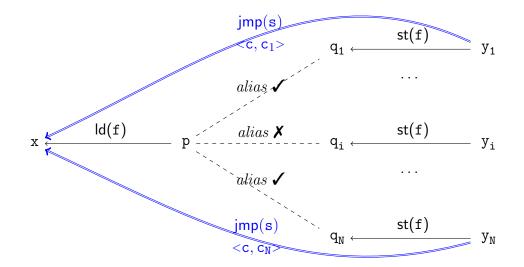

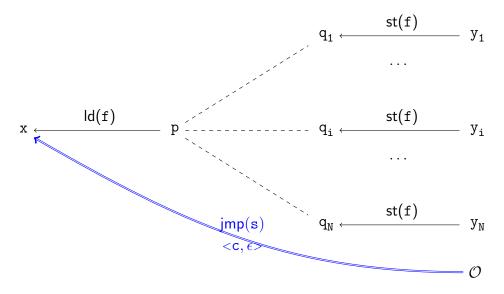

**Data Sharing by Graph Rewriting** We choose to share paths involving heap accesses, which tend to be long (time-consuming to traverse) and common (repeatedly traversed across the queries). As illustrated in Figure 2.4, we do so by avoiding making redundant alias tests in REACHABLENODES(x, c). For its loop at line 18, each iteration starts with a load x = p.f and then examines all the N matching stores  $q_1.f = y_1, \ldots, q_N.f = y_N$  at line 19. For each  $q_k.f = y_k$  accessed in context  $c_k$  such that  $q_k$  is an alias of p,  $(y_k, c_k)$  is inserted into rch, meaning that (x, c) is reachable from  $(y_k, c_k)$  (lines 20 - 24). Note that during this process, mutually recursive calls to POINTSTO(), FLOWSTO() and REACHABLENODES() for discovering other aliases are often made.

There are two cases due to the budget constraint. Figure 3.1(a) illustrates the case when an iteration of line 18 is completely analysed in s steps starting from (x, c) within the pre-set budget. A jmp edge,  $x \xleftarrow{jmp(s)}{\langle c, c_k \rangle} y_k$ , is added for each  $q_k$  that is an alias of p. Instead of rediscovering the path from (x, c) to  $(y_k, c_k)$ , a subsequent query will take this shortcut.

Figure 3.1(b) explains the other case when an iteration of line 18 is only partially analysed since the analysis runs out of budget after s steps have elapsed from (x, c). A special jmp edge,  $x \xleftarrow{jmp(s)}{\langle c, \epsilon \rangle} \mathcal{O}$ , is added to record this situation, where  $\mathcal{O}$  is a special node added and  $\epsilon$  is a "don't-care" context. A later query will benefit from this special shortcut by making an *early termination* (*ET*) if its remaining budget is smaller than s.

Therefore, we have formulated data sharing as a graph rewriting problem by adding jmp edges to the PAG of a program, in terms of the syntax given in Figure 3.2.